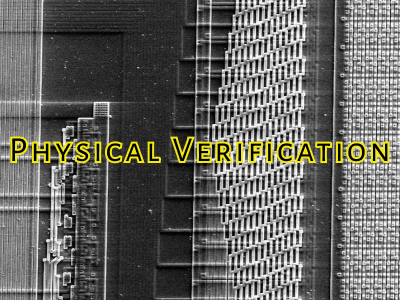

Physical Verification

Physical Verificaiton, is examining your design for all fabrication rules without which fab says no go for manufacturing. It has become to crutial at deep sub micron technologies as number of rules increases exponsially as technolgy node shrinks.

Module 1: Introduction to Physical Verification

- What is Physical Verification?

- Sign-off Flow in ASIC Design

- Importance of DRC, LVS, and ERC

- Overview of Tools: Calibre, PVS, ICV

Module 2: Understanding Foundry Design Rules

- Minimum Width, Spacing, Enclosure

- Layer Stack and Mask Information

- Technology Files and Rule Decks

- Node-specific Challenges (7nm, 16nm, etc.)

Module 3: DRC – Design Rule Check

- Basic Rule Types and Categories

- Most Common Violations and Fixes

- Metal Density and Fill Checks

- Hands-on: Run Calibre DRC and debug violations

Module 4: LVS – Layout vs Schematic

- Netlist Extraction and Comparison

- Shorts, Opens, Missing Devices

- Black-box and Hierarchical LVS

- Parasitic Aware LVS

- Hands-on: Run LVS and fix top violations

Module 5: Antenna Checks

- What is Antenna Effect?

- Layer-based Antenna Violations

- Diode Insertion Strategies

- Foundry Antenna Rules

- Hands-on: Fix antenna violations using diode insertion

Module 6: ERC – Electrical Rule Check

- Power/Ground Connectivity Checks

- Floating Nets, Missing Vias

- Signal Integrity Violations

- Hands-on: Run ERC and debug connectivity

Module 7: Hierarchical Verification

- Top-Down vs Bottom-Up Flow

- Block-level and Full-chip Sign-off

- Handling Placeholders and Black Boxes

- Incremental Sign-off for ECO

Module 8: Tape-out Preparation

- Sign-off Report Review and Documentation

- Checklist for DRC/LVS Clean

- Foundry Sign-off Requirements

- Preparing GDS and LEF/DEF for handoff

Module 9: TCL for Physical Verification Automation

- Writing TCL for Calibre/PVS Execution

- Automating Batch Runs

- Report Parsing and Result Filtering

- Hands-on: Create script for full sign-off job

Module 10: Debug Techniques and Best Practices

- Using RVE and Calibre VIEW

- Annotating Results in Layout Tools (Virtuoso, Innovus)

- Common Pitfalls and their Root Causes

- Debug Strategy in Mass Violations

Module 11: Projects and Labs

- Project 1: DRC + LVS Sign-off for block-level layout

- Project 2: Antenna and ERC clean flow

- Project 3: Full-chip sign-off verification

Tools & Labs

- Mentor Calibre (DRC/LVS/ERC)

- Cadence Pegasus / PVS

- Virtuoso / Innovus Layout Environment

- TCL scripting for flows and reporting

Assessment & Deliverables

- Weekly DRC/LVS exercises

- Final Sign-off Reports Submission

- Project Presentations and Viva

- Certificate on Tape-out Flow Completion

prerequisites

- Basic electronics and Linux basics

- Passion for learning

-

Qualification

- Diploma (EE, EC, EI, CS, IT)

- B.Tech/BE/M.Tech/ME (EE, EC, EI, CS, IT)

- Any degree with Maths and Physics

- Failed students with lots of Passion (Let's work out a way)

Selection Process

- Analytical Test

- Interview